# **Solutions - Final Exam**

(April 18<sup>th</sup> @ 7:00 pm)

Presentation and clarity are very important! Show your procedure!

# PROBLEM 1 (11 PTS)

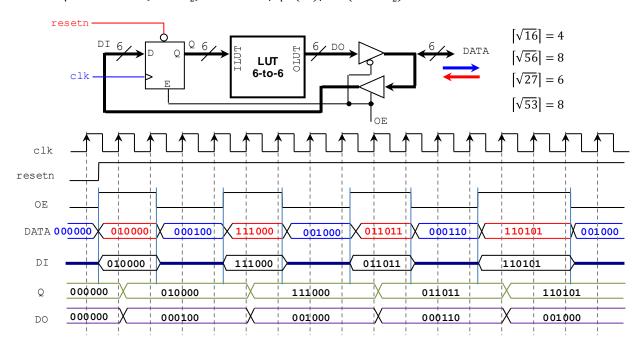

• Given the following circuit, complete the timing diagram. The LUT 6-to-6 implements the following function:  $OLUT = \lceil sqrt(ILUT) \rceil$ , where ILUT is a 6-bit unsigned number. For example  $ILUT = 34 (100010_2) \rightarrow OLUT = \lceil sqrt(34) \rceil = 6 (000110_2)$

## PROBLEM 2 (12 PTS)

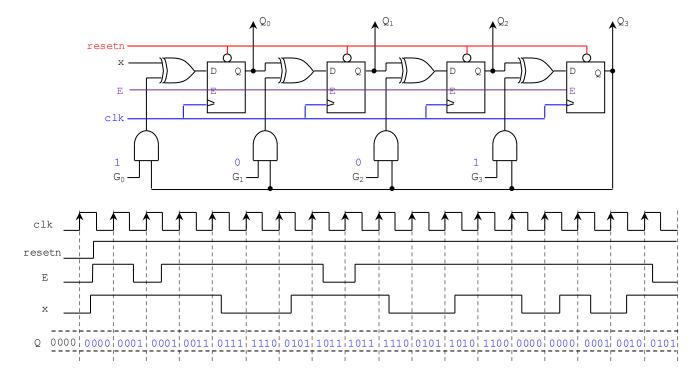

• Complete the timing diagram of the following circuit.  $G = G_3G_2G_1G_0 = 1001$ ,  $Q = Q_3Q_2Q_1Q_0$

#### PROBLEM 3 (22 PTS)

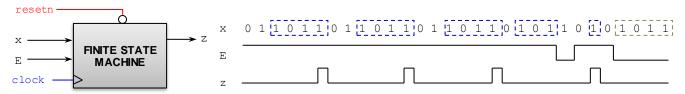

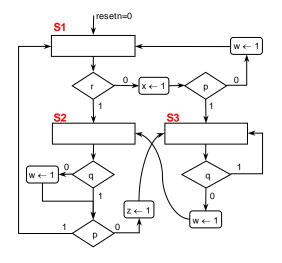

- Sequence detector: The machine has to generate z = 1 when it detects the sequence 1011. Once the sequence is detected, the circuit looks for a new sequence.

- The signal E is an input enable: It validates the input x, i.e., if E = 1, x is valid, otherwise x is not valid.

- Draw the State Diagram (any representation), State Table, and the Excitation Table of this circuit with inputs E and x and output z. Is this a Mealy or a Moore machine? Why? (15 pts)

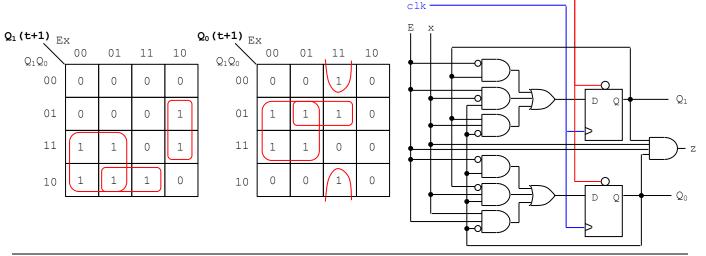

- Provide the excitation equations (simplify your circuit using K-maps or the Quine-McCluskey algorithm) (4 pts)

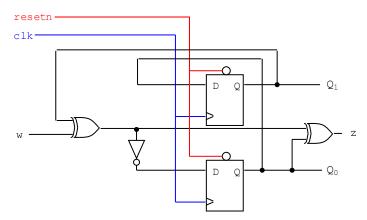

- Sketch the circuit. (3 pts)

- State Diagram, State Table, and Excitation Table:

This is a Mealy Machine. The output 'z' depends on the input as well as on the present state.

Excitation equations, minimization, and circuit implementation:

$$\begin{aligned} Q_1(t+1) &= \bar{E}Q_1 + E\bar{x}Q_0 + xQ_1\overline{Q_0} \\ Q_0(t+1) &= \bar{E}Q_0 + Ex\overline{Q_0} + x\overline{Q_1}Q_0 \\ z &= ExQ_1Q_0 \end{aligned}$$

resetn

## PROBLEM 4 (21 PTS)

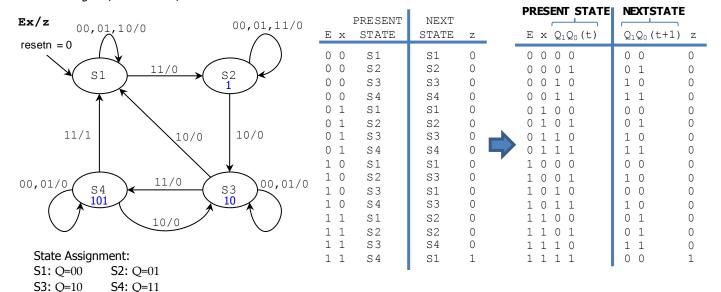

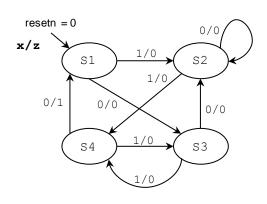

- Given the following State Machine Diagram. (9 pts)

- ✓ Is this a Mealy or a Moore machine? Why?

- $\checkmark$  Get the excitation equations and the Boolean equation for z. Use S1 (Q=00), S2 (Q=01), S3 (Q=10), S4 (Q=11) to encode the states.

| х                               | PRESENT<br>STATE                       | NEXT<br>STATE                                        |                                 |             | _                               | NT STATE | <b>NEXTSTATE</b> Q <sub>1</sub> Q <sub>0</sub> (t+1) z |                                 |                                      |                            |

|---------------------------------|----------------------------------------|------------------------------------------------------|---------------------------------|-------------|---------------------------------|----------|--------------------------------------------------------|---------------------------------|--------------------------------------|----------------------------|

| 0<br>0<br>0<br>0<br>1<br>1<br>1 | S1<br>S2<br>S3<br>S4<br>S1<br>S2<br>S3 | \$3<br>\$2<br>\$2<br>\$1<br>\$2<br>\$4<br>\$4<br>\$3 | 0<br>0<br>0<br>1<br>0<br>0<br>0 | <b>&gt;</b> | 0<br>0<br>0<br>0<br>1<br>1<br>1 | 0 0 1    | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1                   | 1<br>0<br>0<br>0<br>0<br>1<br>1 | 0<br>1<br>1<br>0<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>1<br>0<br>0 |

$$Q_1(t+1) \leftarrow x \oplus (Q_1(t) + Q_0(t))$$

$$Q_0(t+1) \leftarrow \left(Q_1(t) \oplus Q_0(t)\right) + x \overline{Q_0(t)}$$

$$z = \bar{x}Q_1(t)Q_0(t)$$

This is a Mealy Machine. The output 'z' depends on the input as well as on the present state.

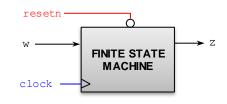

- The following FSM has 4 states, one input w and one output z. (12 pts)

- ✓ The excitation equations are given by:

$$Q_1(t+1) \leftarrow Q_0(t)$$

$$\begin{array}{cc} & Q_1(t+1) \leftarrow \underline{Q_0(t)} \\ & Q_0(t+1) \leftarrow \overline{Q_1(t)} \oplus w \end{array}$$

- ✓ The output equation is given by:  $z = Q_1(t) \oplus Q_0(t) \oplus w$

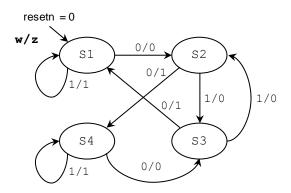

- ✓ Provide the State Diagram (any representation) and the Excitation Table.

- ✓ Sketch the Finite State Machine circuit.

| PRESENT STATE  W Q <sub>1</sub> Q <sub>0</sub> (t) | NEXTSTAT $Q_1Q_0$ (t+1) | _ |   | W | PRESENT<br>STATE | NEXT<br>STATE | Z |

|----------------------------------------------------|-------------------------|---|---|---|------------------|---------------|---|

| 0 0 0                                              | 0 1                     | 0 | • | 0 | S1               | S2            | 0 |

| 0 0 1                                              | 1 1                     | 1 |   | 0 | S2               | S4            | 1 |

| 0 1 0                                              | 0 0                     | 1 |   | 0 | S3               | S1            | 1 |

| 0 1 1                                              | 1 0                     | 0 |   | 0 | S4               | S3            | 0 |

| 1 0 0                                              | 0 0                     | 1 | 4 | 1 | S1               | S1            | 1 |

| 1 0 1                                              | 1 0                     | 0 |   | 1 | S2               | s3            | 0 |

| 1 1 0                                              | 0 1                     | 0 |   | 1 | S3               | S2            | 0 |

| 1 1 1                                              | 1 1                     | 1 |   | 1 | S4               | S4            | 1 |

## PROBLEM 5 (16 PTS)

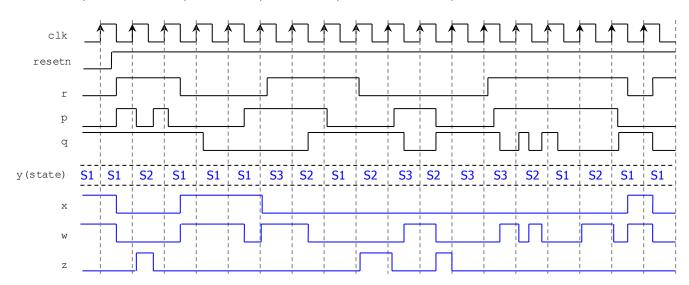

- Draw the State Diagram (in ASM form) of the FSM whose VHDL description in shown below. Is it a Mealy or a Moore FSM?

- Complete the Timing Diagram.

```

library ieee;

use ieee.std_logic_1164.all;

entity circ is

port ( clk, resetn: in std_logic;

r, p, q: in std_logic;

x, w, z: out std_logic);

end circ;

```

```

architecture behavioral of circ is

type state is (S1, S2, S3);

signal y: state;

begin

Transitions: process (resetn, clk, r, p, q)

begin

if resetn = '0' then y <= S1;

elsif (clk'event and clk = '1') then

case y is

when S1 =>

if r = '1' then

y <= S2;

else

if p = '1' then y \le S3; else y \le S1; end if;

end if;

when S2 =>

if p = '1' then y \le S1; else y \le S3; end if;

when S3 =>

if q = '1' then y \le S3; else y \le S2; end if;

end if;

end process;

Outputs: process (y, r, p, q)

begin

x <= '0'; w <= '0'; z <= '0';

case y is

when S1 \Rightarrow if r = 0' then

x <= '1';

if p = '0' then

w <= '1';

end if;

end if;

when S2 \Rightarrow if q = '0' then w <= '1'; end if;

if p = '0' then z \le '1'; end if;

when S3 \Rightarrow if q = '0' then w <= '1'; end if;

end case;

end process;

end behavioral;

```

This is a Mealy Machine. The outputs 'x,w,z' depend on the input as well as on the present state.

4

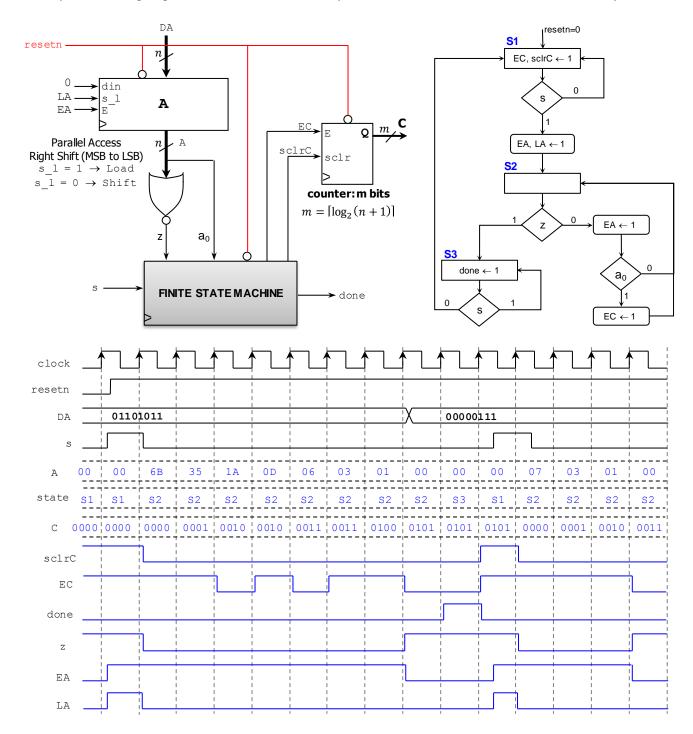

# **PROBLEM 6 (18 PTS)**

- "Counting 1's" Circuit: It counts the number of bits in register A that has the value of '1'.

The digital system is depicted below: FSM + Datapath. Example: For n = 8: if A = 00110110, then C = 0100.

✓ m-bit counter: If E = sclr = 1, the count is initialized to zero. If E = 1, sclr = 0, the count is increased by 1.

- ✓ Parallel access shift register: If E = 1:  $s_{-}l = 1 \rightarrow \text{Load}$ ,  $s_{-}l = 0 \rightarrow \text{Shift}$ .

- Complete the timing diagram where n = 8, m = 4. A is represented in hexadecimal format, while C is in binary format.

5

Instructor: Daniel Llamocca